SpaceWire UK

Specialist providers of VHDL Intellectual Property & Design Services

icon in the Diagram pane inside the BLOCK DESIGN section.

icon in the Diagram pane inside the BLOCK DESIGN section.

Click OK to commit the changes.

Click OK to commit the changes.

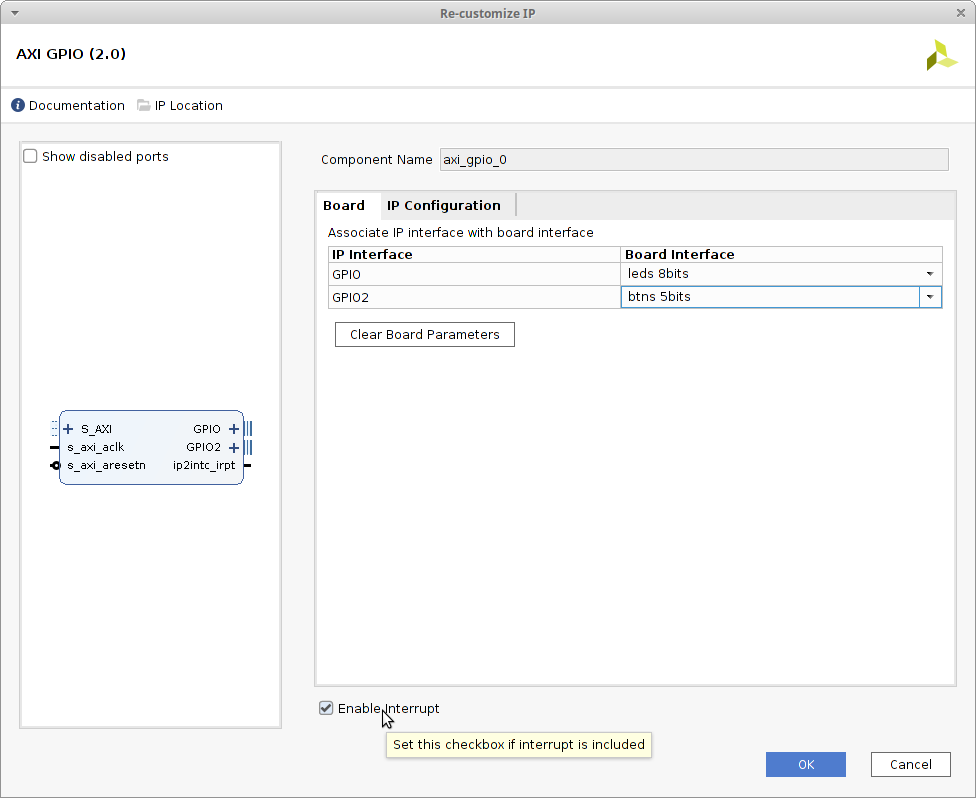

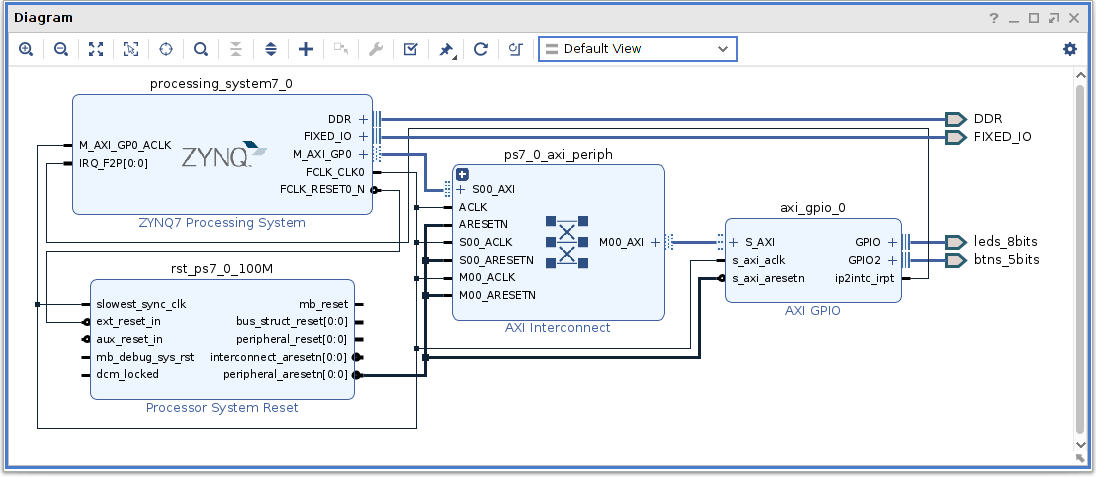

Connection to the interrupt output ip2intc_irpt on the AXI GPIO is required for this design. To enable this tick Enable Interrupt.

Connection to the interrupt output ip2intc_irpt on the AXI GPIO is required for this design. To enable this tick Enable Interrupt.

Click OK to commit the changes.

Click OK to commit the changes.

icon. Once validated save the block design and return the floating Diagram pane back to Vivado by clicking on the Dock

icon. Once validated save the block design and return the floating Diagram pane back to Vivado by clicking on the Dock  icon.

icon.